# Fault Analysis Based on Integration of Digital Relay and DFR Data

X. Luo, Student Member, IEEE, and M. Kezunovic, Fellow, IEEE

*Abstract*—This paper discusses integration of two existing automated analysis applications, DFR Data Analysis and Digital Relay Data Analysis, to achieve comprehensive fault analysis. As inputs to the integrated application, digital relay files and reports are introduced. The proposed strategy and implementation of integration are outlined. An example is used to demonstrate features of the integrated application developed so far.

*Index Terms*— digital relay, IED, expert system, fault analysis, data integration

## I. INTRODUCTION

THE history of automated fault analysis dates back to the late eighties when first expert systems for automated analysis were introduced [1]. In the last two decades, various expert system applications for fault analysis have been reported in literature [2], [3], [4]. Most of these applications rely on rule based expert system techniques to perform disturbance analysis and validation of protection system operation using sequence of events recorders (SER), digital fault recorders (DFR) and supervisory control and data acquisition (SCADA) systems as sources of relevant field data.

Reference [5] presents an expert system based DFR Data Analysis (DFRDA) application for automated fault analysis. In this application, analog waveforms as well as statuses of relay and circuit breaker contacts recorded by DFRs are used to analyze disturbance events and protection system operation. Evaluation and test carried out at Center Point Energy Company in Houston proves that this application is quite successful [6]. However, only limited behavior of protection systems is analyzed in this application. This is due to the fact that DFRs can not provide detailed information of internal states of protection system components, especially relays.

Due to the power of microprocessors, many modern digital protective relays can provide users with abundant data about what relays "see" and how they respond during power system faults. These data include not only sampled analog currents and voltages but also status of input and output contacts, which are acquired by fault recording function. Also, statuses of protection elements and logic operands, which reveal detailed internal behavior of relays, are recorded [7]. The data are usually contained in various relay files and reports such as oscillography file, setting file, fault report and event report. Recently, an expert system based Digital Protective Relay Data Analysis (DPRDA) application has been developed to perform validation and diagnosis of digital relay operation in great detail by analyzing relay files and reports [8]. The analysis is partially based on disturbance information provided by a disturbance event analysis function, which is not included in the DPRDA application currently.

Based on evaluation of DFRDA and DPRDA applications, a strategy of combining the two applications to perform comprehensive fault analysis based on relay files and reports are proposed in this paper. Section II introduces files and reports of modern digital relays, which provide fundamental information for fault analysis. Section III details the strategy of fault analysis based on integration of the two applications. Then Section IV discusses implementation issues of integration. Section V presents an example to illustrate features of the integrated application developed so far. Finally, conclusions and proposals for future work are given in Section VI.

#### II. FILES AND REPORTS OF DIGITAL RELAYS

Modern digital relays are capable of generating various files and reports, each of which may address a specific purpose. Generally, an oscillography file records what a relay "sees" during disturbance events. A setting file specifies how the relay is configured. A fault report presents parameters calculated by the relay for its decision making. An event report reveals how the relay actually responds to the disturbance events according to its decision. It is also worth mentioning that in order to achieve maximum flexibility, the firmware of many digital relays is designed as functions by employing Object-Oriented Design and Programming techniques. These functions usually are input and output contacts, protection elements, control elements and pilot schemes. In relay files and reports, the states of each function are represented by a set of predefined logic operands [9], [10]. Four common relay files and reports are introduced as follows.

## A. Oscillography File

An oscillography file is usually in COMTRADE format [11]. It is generated by the fault recording function of a digital relay. Nowadays the fault recording function of many digital relays is quite powerful. For example, GE's D60 relay can record up to 16 analog channels and 64 digital channels at a sampling rate of

This work was supported by PSerc Project T-17 "Enhanced Reliability of Power System Operation Using Advanced Algorithms and IEDs for On-Line Monitoring".

X. Luo and M. Kezunovic are with the Department of Electrical Engineering, Texas A&M University, College Station, TX 77843-3128, USA (e-mails: xuluo@ee.tamu.edu, kezunov@ee.tamu.edu)

64 samples per cycle. The data in several oscillography files can be concatenated to achieve even longer recording time [9]. Since the recording capability of many digital relays is comparable to that of specialized DFRs, applying the algorithms of DFRDA application on the oscillography data of a digital relay is feasible and justifiable.

It should also be mentioned that an advantage of fault recording function of a digital relay over a DFR is that the status of any logic operand can be recorded as a digital channel. That is to say, status of both external contacts and internal states of a digital relay can be recorded in its oscillography file while the digital channels of a DFR can only record the status of external contacts.

# B. Setting File

A setting file contains configuration information of a relay. Usually a setting file configures the relay at three levels: selecting protection and control elements, deciding how the selected elements are logically combined and setting operating parameters of each selected element. The three levels of information are used in DPRDA application to determine the expected relay behavior.

# C. Fault Report

A fault report usually contains information of fault type, fault location and voltage and current phasors during pre-fault and fault periods. The information is provided by the relay itself. Whether the fault type and fault location information produced by a relay can be used to verify protection operation of the relay itself depends on two preconditions. First, the fault classification and fault location algorithms of the relay should be independent from its protection algorithms. Otherwise it is unreasonable to use the result of one of two related algorithms as reference to verify the result of the other. Secondly, the fault classification and fault location algorithms should be accurate enough. If the two preconditions can't be satisfied, an external source of disturbance information based on advanced algorithms and techniques should be used instead of the information provided by the relay [5], [12], [13]. In discussion of this paper, the DFRDA application serves as the external source of information.

### D. Event Report

An event report is a list of time-stamped logic operands in chronological order. It contains most of the information through which the external operation and internal states of a digital relay can be observed. According to our investigation, for some types of relays, not all active logic operands that may be important for analysis are reflected in the event reports. This problem can be solved if users select these operands to be recorded in the oscillography file of the relay.

It should be noticed that relay performance specification in user's manuals also provides useful information of elements' operating parameters for predicting relay behavior. For example, a performance specification for a phase distance element may be its average operating time for Zone 1.

# III. STRATEGY OF FAULT ANALYSIS BASED ON INTEGRATION

#### A. Conceptual Strategy of Integration

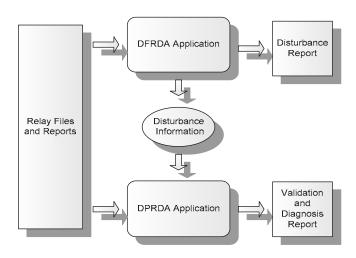

The underlying idea of integration of DFRDA and DPRDA applications is that the algorithms for DFRDA application are used to perform detailed disturbance event analysis based on the data in COMTRADE oscillography file generated by fault recording function of a relay, while the algorithms for DPRDA application are taken to perform detailed validation and diagnosis of relay operation based on the results of disturbance event analysis and the data from all the relay files and reports. Fig. 1 illustrates the conceptual strategy of integration.

As introduced in Section I, DFRDA application can perform detailed disturbance analysis [5]. The disturbance information provided by the original DFRDA application includes fault detection, fault inception time, fault type, circuit breaker current interruption detection and circuit breaker current interruption time. A new fault location algorithm based on synchronized sampling at two ends of lines has been adopted during the later improvements [13]. Since only a few external contact signals such as relay trip signal, communication signal and circuit breaker contact signal are recorded by DFRs, the DFRDA application only performs simple analysis of protection system operation.

On the other hand, DPRDA application can perform detailed analysis of protection system operation because its analysis is based on abundant data, which reflect both the external contact status of a relay and its associated circuit breaker and the internal element status of the relay [8]. The analysis results not only include validation of correctness of phase operation, relay trip operation, circuit breaker opening and circuit breaker current interruption, but also include the reasons for certain failure and missoperation. A deficiency of the current DPRDA application is that its analysis needs external disturbance information.

As we can see, the DFRDA application and DPRDA application are actually complementary to each other and their integration may overcome their individual deficiencies and result in a comprehensive fault analysis application.

Fig. 1. Conceptual strategy of integration of two applications

# B. Modules of the Integrated Application

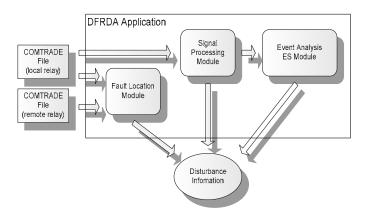

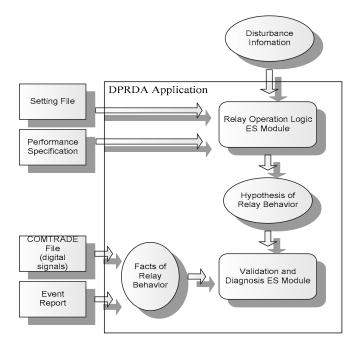

The integration application is composed of several modules which come from DFRDA and DPRDA applications. As shown in Fig.2, DFRDA application consists of Signal Processing Module, Event Analysis Expert System Module and Fault Location Module. Fig. 3 shows that DPRDA application includes Relay Operation Logic Expert System Module and Validation and Diagnosis Expert System Module.

Signal Processing Module takes oscillography data contained in a COMTRADE file of the relay. It first distinguishes the pre-fault, fault, and post-fault time intervals of voltages and currents. Then the RMS values of voltages and currents as well as the zero sequence values of currents for the three time intervals are calculated. During the calculation, the fault inception time and circuit breaker current interruption time may be decided.

The Event Analysis Expert System Module takes the signal parameters extracted from the Signal Processing Module as inputs. It performs forward chaining reasoning to analyze the relationship of RMS values of voltages and currents to detect the fault and classify the fault type. It also uses the values of zero sequence currents and fault detection information to detect current interruption by the circuit breaker.

Fault Location Module uses oscillography data from COMTRADE files of both the local relay and the remote relay to calculate fault location based on synchronized sampling technique.

Based on the analysis results from modules of DFRDA application, a disturbance report will be generated. It generally includes disturbance information such as fault inception time, fault location, fault type, circuit breaker current interruption time.

The disturbance information, along with data in the relay setting file and performance specification, is taken into Relay Operation Logic Expert System Module to predict status and timing of each active logic operand of the relay by performing forward chaining reasoning.

The actual status and timing of logic operands are obtained from the event report and the digital portion of osillography file. With both hypothesis and facts of relay behavior as inputs, Validation and Diagnosis Expert System Module first performs

Fig. 2. Functional modules of DFRDA application

Fig. 3. Functional modules of DPRDA application

validation of correctness of relay operation based on hypothesis-fact matching, and then the diagnosis of the reasons for certain failure and missoperation is obtained using backward chaining reasoning [14]. Finally a report on the results of validation and diagnosis will be generated.

As discussed above, comprehensive fault analysis is achieved by the integrated application. The analysis results, which include detailed information of both power system disturbance and protection system operation, can serve different user groups. System operators may conduct system restoration after faults based on the disturbance information. Protection engineers may use the validation and diagnosis information of protection system operation to evaluate performance, identify component deficiencies and trace possible reasons for black outs.

# IV. IMPLEMENTATION OF THE INTEGRATION

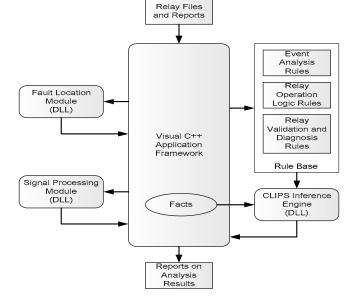

As discussed in Section II, both DFRDA and DPRDA applications are developed using modular concept by employing Object-Oriented techniques. An efficient way to integrate the two applications is to embed the modules of one application into the other. Our proposed approach is to embed the modules of DFRDA application into DPRDA application.

#### A. Implementation Architecture

The framework of DPRDA application is developed under the platform of Visual C++. The CLIPS expert system inference engine is linked with the framework by means of Dynamic Link Library (DLL). The framework mainly takes care of loading facts and rules into the inference engine and reading the inference results from the engine.

Since the Event Analysis Expert System Module of DFRDA application is also developed in CLIPS expert system shell [14], it can directly use the inference engine in DPRDA application. The Signal Processing Module and Fault Location Module of DFRDA application are originally developed using MATLAB M-file programming language, which makes it difficult to directly link them with the framework of DPRDA application. To solve the problem, a convenient way is to use the MATLAB C Code Generation Toolbox to convert the M-file Codes into C code and make the two modules as Dynamic Link Library (DLL) to link with the framework of DPRDA application. Fig. 4 illustrates the implementation structure of the integrated application.

# B. Program Execution Process

In Fig.4, the application framework serves as an interface for all the functional modules as well as inputs and outputs of the application. It first reads in oscillography data from the COMTRADE file and calls Fault Location DLL and Signal Processing DLL to process these data. The processing results are sent back to the framework. Then CLIPS Inference Engine DLL is called and results from Signal Processing DLL together with event analysis rules are loaded into the CLIPS Inference Engine. The inference results for event analysis along with fault location result and some signal processing results constitute disturbance information. At this point, the framework further reads in relevant data from relay setting file and performance specification. After CLIPS Inference Engine DLL is called again, these data and disturbance information together with relay operation logic rules are loaded into CLIPS Inference Engine to predict relay behavior. Finally, the framework reads in data which represent actual relay behavior from the event report and the digital portion of COMTRADE file and loads them into CLIPS Inference Engine together with validation and diagnosis rules. The inference results are information of validation and diagnosis of protection system operation.

In this section we use an example to demonstrate some features of the proposed integrated application. Since currently the integration of modules of DFRDA application into DPRDA application has not yet been completed, we will make assumptions about the outputs of Signal Processing Module, Fault Location Module and Event Analysis Expert System Module, then use a modified graphic user interface (GUI) of DPRDA application to demonstrate the example.

# A. Simulation Procedure

We first set up simulation in a laboratory to get the relay reports and files to be analyzed, which is shown in Fig. 5.

ATP program is used to simulate the disturbance event. Then a commercial software called RELAY ASSISTANT is used to convert the ATP data file in PL4 format into COMTRADE format and download it to the relay test set [15]. The simulated signals are generated by the relay test set and input to the relay to be tested. This triggers the relay to operate and generate files and reports. These reports and files are automatically read into the fault analysis application.

It should be mentioned that the contact signal of circuit breaker associated with the relay is simulated using a logic operand signal and a timer inside the relay. The timing of the contact signal is set to match the event simulated in ATP program.

# B. Relay Files and Reports

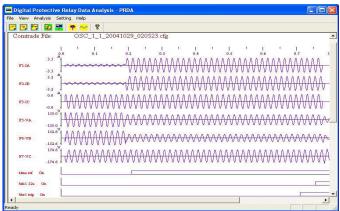

The disturbance event is caused by an A-B-G fault. Fig. 6 shows the oscillography file displayed in the GUI of DPRDA application. TABLE I is the list of disturbance information which is set as the simulation parameters in ATP program.

It should be noticed that in this example we assume that the modules of DFRDA application has generated the same disturbance information as listed in TABLE I so that DPRDA application can directly use the information.

Fig.4. Implementation architecture of the integrated application for comprehensive fault analysis

Fig. 5. Simulation procedure to get relay files and reports

Fig. 6. Oscillography file

TABLE I DISTURBANCE INFORMATION

| Fault Type                    | A-B-G        |

|-------------------------------|--------------|

| Fault Location                | Zone 2       |

| Fault Inception Time          | 0.18 second  |

| CB Currents Interruption      | Succeeded    |

| CB Currents Interruption Time | 0.764 second |

Corresponding to the fault, the relay and associated circuit breaker should behave as expected according to the relay setting and performance specification. The relay setting file is automatically read into the DPRDA application. The performance specification is manually input into a dialog shown in Fig. 7.

According to the relay setting and performance specification, Phase Distance Zone 2 Element and Ground Distance Zone 2 Element should operate to make the relay trip at 0.502 second and the circuit breaker should open at 0.550 second.

The actual relay and circuit breaker behavior in terms of status and timing of relay logic operands are recorded in the event report. Fig. 8 shows a portion of the report displayed in the GUI of DPRDA application. It should be noticed that we have deliberately manipulated the event report to introduce some failures and missoperation so that the analysis capability of the application can be demonstrated comprehensively.

| PHASE DIST            | PHASE TOC       | PHASE IOC       | CIRCUIT BREAKER  |

|-----------------------|-----------------|-----------------|------------------|

| SUPN DELAY 0.001      | PKP DELAY 0.001 | PKP DELAY 0.001 | OPEN DELAY 0.048 |

| PKP DELAY 0.001       | OP SPEED 0.004  | OP SPEED 0.004  | OPEN SPEED 0.008 |

| DP DELAY 0.02         |                 |                 | INTR DELAY 0.064 |

| OP SPEED 0.004        |                 |                 | INTR SPEED 0.008 |

| GROUND DIST           | GROUND TOC      | GROUND IOC      |                  |

| SUPN DELAY 0.002      | PKP DELAY 0.002 | PKP DELAY 0.002 |                  |

| PKP DELAY 0.001       | OP SPEED 0.004  | OP SPEED 0.004  |                  |

| OP DELAY 0.02         | TOLERANCE       | TOLEMANCE       |                  |

| OP SPEED<br>TOLERANCE |                 |                 |                  |

|                       |                 |                 |                  |

Fig. 7. Relay and circuit breaker performance specification dialog

| e View Analysis Set |                            |                      |  |

|---------------------|----------------------------|----------------------|--|

| 3 🖻 🖻 🖗 👎           |                            |                      |  |

| Event Record File:  | EVT_1_20041029_020518.evt  |                      |  |

| Event Number        | Date/Time                  | Cause                |  |

| 1                   | 10/29/2004,02:05:18.609047 | EVENTS CLEARED       |  |

| 2                   | 10/29/2004,02:10:33.922088 | PHASE IOC1 PKP B     |  |

| 3                   | 10/29/2004,02:10:33.922088 | OSCILLOGRAPHY TRIG'D |  |

| 4                   | 10/29/2004,02:10:33.924170 | PHASE IOC1 PKP A     |  |

| 5                   | 10/29/2004,02:10:33.924170 | PH DIST Z1 SUPN IAB  |  |

| 6                   | 10/29/2004,02:10:33.926252 | PH DIST Z1 SUPN IBC  |  |

| 7                   | 10/29/2004,02:10:33.926252 | PH DIST Z1 SUPN ICA  |  |

| 8                   | 10/29/2004,02:10:33.926252 | PH DIST Z3 PKP AB    |  |

| 9                   | 10/29/2004,02:10:33.926252 | PH DIST Z3 SUPN IAB  |  |

| 10                  | 10/29/2004,02:10:33.926252 | PH DIST Z2 PKP AB    |  |

| 11                  | 10/29/2004,02:10:33.926252 | PH DIST Z2 SUPN LAB  |  |

| 12                  | 10/29/2004,02:10:33.928336 | PH DIST Z3 PKP BC    |  |

| 13                  | 10/29/2004,02:10:33.928336 | PH DIST Z3 PKP CA    |  |

| 14                  | 10/29/2004,02:10:33.928336 | PH DIST Z3 SUPN IBC  |  |

| 15                  | 10/29/2004,02:10:33.928336 | PH DIST Z2 PKP CA    |  |

| 16                  | 10/29/2004,02:10:33.928336 | PH DIST Z2 SUPN IBC  |  |

| 17                  | 10/29/2004,02:10:33.928336 | PH DIST Z2 SUPN ICA  |  |

| 18                  | 10/29/2004,02:10:33.928336 | PH DIST Z3 SUPN ICA  |  |

| 19                  | 10/29/2004,02:10:34.421766 | PHASE IOC1 OP B      |  |

| 20                  | 10/29/2004 02:10:34 421766 | hkr1 trin On         |  |

Fig. 8. Event report

When performing analysis, the absolute time for each logic operand in the event report is converted to relative time with respect to the fault inception time.

# C. Results of Validation and Diagnosis

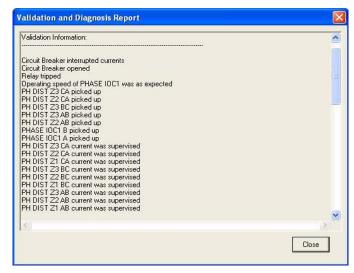

The results are displayed in the dialog shown in Fig. 9 (a) and Fig. 9 (b) respectively.

As we can see in the validation information section, PHASE IOC Element operated to make the relay trip. The circuit breaker opened because of the relay trip and the fault currents were interrupted by the circuit breaker.

Several failures and misoperation were identified as shown in the diagnosis information section. Ground Distance Zone 2 element and Ground Distance Zone 3 element should have picked up but failed to pick up because their neutral current supervising failed. The neutral current supervising of Ground Distance Zone 1 element also failed. In addition, Ground IOC element failed to pick up. From the diagnosis information for ground elements, we may know that it is highly possible that something is wrong with the neutral current channel.

Because Phase Distance Zone 2 element should have operated but failed to operate, it was the Phase IOC element instead of Phase Distance Zone 2 element that made the relay trip. From such information, we may know that Phase IOC element functioned correctly as a backup for distance elements. Since the operating time delay of Phase IOC element was set to be longer than that of Phase Distance Zone 2 element, the relay trip was delayed. The reason for failure of operation of Phase Distance Zone 2 was that its CA and AB phase elements picked up but failed to operate and its BC phase element even failed to pick up.

Further more, there was timing diagnosis information related to circuit breaker. The circuit breaker opened a little bit faster than expected but within pre-set tolerance. However, it interrupted currents slower than expected. The delay was out of the pre-set tolerance.

All the validation and diagnosis information is as expected, which proves the correctness of the design of the application.

Fig. 9 (a). Validation information

# Validation and Diagnosis Report Diagnosis Information: ~ GND DIST Z1 neutral current supervision failed <- GND DIST Z1 Neutral Current Supervising Component malfunctioned GND DIST Z2 A failed to pick up <- GND DIST Z2 neutral current supervision failed <- GND DIST Z2 Neutral Current Supervising Component malfunctioned GND DIST Z2 B failed to pick up <- GND DIST Z2 neutral current supervision failed <- GND DIST Z2 Neutral Current Supervising Component malfunctioned GND DIST Z3 A failed to pick up <- GND DIST Z3 neutral current supervision failed <- GND DIST Z3 Neutral Current Supervising Component malfunctioned GND DIST Z3 B failed to pick up <- GND DIST Z3 neutral current supervision failed <- GND DIST Z3 Neutral Current Supervising Component malfunctioned GROUND IOC1 failed to pick up GROUND IOC1 Pickup Component malfunctioned Relay was tripped by incorrect element As a subped by incorrect element A Relay should have been tripped by PH DIST Z2 but it was tripped by PHASE IOC1 \*\* A Relay should have been tripped by PH DIST Z2 but it was tripped by PHASE IOC1 \*\* All the phases of PH DIST Z2 expected to operate failed to operate \*\*\*\*\* All the phases of PH DIST Z2 be called to prevate All the phases of PH DIST Z2 be called to prevate All the phases of phase the phase of phase because the phase the phase because the phase PH DIST Z2 BC Pickup Component malfunctioned \*\*\*\* <- PH DIST Z2 CA failed to operate <- PH DIST Z2 CA Operation Component malfunctioned \*\*\*\* <- PH DIST Z2 AB failed to operate <- PH DIST Z2 AB Operation Component malfunctioned Circuit Breaker interrupted currents slower than expected by 0.019880 second and out of tolerance Circuit Breaker opened faster than expected by 0.002167 second and in tolerance

Fig. 9 (b). Diagnosis information

### VI. CONCLUSION

Based on the discussion in this paper, conclusions are drawn as follows:

• Various reports and files generated by digital protective relays provide abundant information for comprehensive fault analysis.

• Expert system is a very promising artificial intelligence technique for developing automated analysis applications to power system.

• Integration of existing fault analysis applications though data integration and information exchange is an effective way to gain improvements of analysis capability.

Future work will be related to embedding modules of DFRDA application into DPRDA application. Further more, another existing analysis application based on expert system technique, the Circuit Breaker Monitoring application [16] may also be integrated with DFRDA application and DPRDA application to achieve even more comprehensive fault analysis.

# REFERENCES

- [1] M. Kezunovic, C.C. Liu, J. McDonald, L.E. Smith, Automated Fault Analysis, IEEE Tutorial, IEEE PES, 2000.

- [2] M. Meri, "An expert system for disturbance analysis validation and verification", Third Symposium on Expert Systems Application to Power Systems, Tokyo/Kobe, Japan, April 1992.

- [3] S. D. J. Macarthur, J. R. McDonald, S. C. Bell, "Expert systems and model based reasoning for protection performance analysis", *Artificial Intelligence Applications in Power Systems, IEE Colloquium on*, April 20, 1995.

- [4] D. G. Esp, "Real-time fault analysis for transmission systems", Artificial Intelligence Techniques in Power Systems, IEE Colloquium on, Nov. 3, 1997, pp. 5/1 - 5/4.

- [5] M. Kezunovic, P. Spasojevic, C. Fromen, D. Sevcik, "An expert system for transmission substation event analysis", *IEEE Trans. Power Delivery*, vol. 8, no. 4, pp. 1942-1949, October 1993.

- [6] Kezunovic, I. Rikalo, C. Fromen, "Expert system reasoning streamlines disturbance analysis", *IEEE Computer Applications in Power*, vol. 7, No. 2, pp. 15-19, April 1994.

- [7] D. Costello, "Understanding and analyzing event report information", technical paper, Schweitzer Engineering Laboratories, Inc., Pullman, WA, 2000, Available: http://www.selinc.com/techpprs.htm.

- [8] M. Kezunovic, X. Luo, "Automated analysis of protective relay data", 18th International Conference on Electricity Distribution – CIRED, Turin, Italy, June 2005.

- [9] *Instruction Manual for D60 Line Distance Relay*, General Electric Company, Fairfield, CT, 2004.

- [10] Instruction Manual for SEL421 High-Speed Line Protection, Automation, and Control System, Schweitzer Engineering Laboratories, Inc., Pullman, WA, 2004.

- [11] IEEE Common Format for Transient Data Exchange (COMTRADE) for Power Systems, IEEE Standard, 1999.

- [12] S. Vasilic, M. Kezunovic, "An improved neural network algorithm for classifying the transmission line faults", IEEE PES Winter Meeting, New York, Jan 2002.

- [13] M. Kezunovic, B. Perunicic, "Automated transmission line fault analysis using synchronized sampling at two ends", *IEEE Trans. Power Systems*, vol. 11, no. 1, pp. 441-447, February 1996.

- [14] J. Giarratano, G. Riley, *Expert Systems Principles and Programming*, PWS Publishing Company, Boston, 1994, pp. 158-165.

- [15] Primer for PC-Based Simulator for Relay Testing, Test Laboratories International, Inc., College Station, TX, 2002.

- [16] M. Kezunovic, Z. Ren, G. Latisko, D.R. Sevcik, J. Lucey, W. Cook, E. Koch, "Automated monitoring and analysis of circuit breaker operation", *IEEE Transactions on Power Delivery* (Accepted, In Press).

**Xu Luo** (S'05) received his B.E. and M.E. degrees from Xi'an Jiaotong University, Xi'an, China, both in electrical engineering in 1999 and 2002 respectively. He has been with Texas A&M University pursuing his Ph.D. degree since Aug. 2002. His research interests are power system protection, substation automation and artificial intelligence applications in Power System protection.

**Mladen Kezunovic** (S'77, M'80, SM'85, F'99) received his Dipl. Ing. Degree from the University of Sarajevo, the M.S. and Ph.D. degrees from the University of Kansas, all in electrical engineering, in 1974, 1977 and 1980, respectively. He has been with Texas A&M University since 1987 where he is the Eugene E. Webb Professor and Director of Electric Power and Power Electronics Institute. His main research interests are digital simulators and simulation methods for equipment evaluation and testing as well as application of intelligent methods to control, protection and power quality monitoring. Dr. Kezunovic is a registered professional engineer in Texas, and a Fellow of the IEEE.