Dale I. Rummer

Mladen Kezunovic

University of Kansas Electrical Engineering Department Lawrence, Kansas 66845

MLADER REZULCVIO

## ABSTRACT

Much good work has been done over the past decade on the development of digital computer based methods for the protection of electric power systems. The application of these Computer Relaying (CR) systems was not cost effective because the available computer equipment dictated a serial solution to what is in essence a parallel problem. The recent development of low cost, but very capable, microcomputers makes possible the consideration of a network of microcomputers as a cost effective way to implement CR systems. This paper considers the design of a Distributed Processing Microprocessor Based Hierarchically Structured (DMH) system for the protection of electric power systems. Some basic characteristics of the process of power system protection are analyzed. Considerations related to this new system concept are stated and the basic logical structure of the DMH system is described. Specifications are proposed for the necessary computer haidware, and a brief evaluation of available microcomputers relative to these specifications is given. Expected performance of the proposed DMH system is discussed and suggestions for further work are outlined.

## I. INTRODUCTION

As the complexity and the level of transmission voltages of the power systems increase, the importance of the protection function within the overall functioning of the power system is increasingly becoming a popular issue. The cost of protection equipment is also an inseparable issue which comes into any considerations related to power system protection.

Reflecting all other relevant issues, the importance and the cost of the protection function have challenged the people at the utility companies, research institutions and universities to adopt the newest technologies and to develop improved methods and equipment for protection. CR is developing as a result of these efforts.

Specific performances of digital computers were recognized by researchers concerned with power protection applications sometime in the late 60's. Since that time, around 100 technical papers and publications [1,2,3] have been written on the subject and a number of research projects completed at the utility companies, research institutions and universities. Very few publications [4,5,6,7,8,9,10] have considered the applications of microprocessors to the CR field.

Our intentions in this paper are to induce a new concept that could be applied to (form several protection functions within the power system, namely the DMH concept. In Section 2 some basic considerations of the protection task within the power system from the point of view of the DMH concept are analyzed. The basic logical characteristics of the DMH system are introduced in Section 3. In Section 4 specifications for system hardware are proposed and evaluation of available computer hardware relative to these specifications given. Section 5 gives some conclusions and some new ideas for further research activities.

## II. SOME BASIC CONSIDERATIONS OF THE PROTECTION FUNCTION AS THEY ARE RELATED TO THE DNH CONCEPT

In this section the following protection systems will be considered:

-"classical" relaying systems (electromechanical and static relays)

-Computer Based Relaying (CBR) systems

-Microprocessor Based Relaying (MBR) systems

Terms CBR and MBR are introduced in this section in order to distinguish between two classes of computer systems used as protection systems: large computer systems (at least minicomputers) and microprocessor computer systems (microcomputers).

All three basic systems mentioned above will be compared and discussed through the discussion of several basic requirements of any system:

- Utilization, or the percentage of time the system is efficiently used.

- Accuracy, or ability to give an optimum response to a certain set of conditions.

- Speed, or the ability to react quickly to a change in the inputs.

- Flexibility, or the ability to adapt to functional changes.

- Reliability, or the ability to provide predetermined changes in the outputs given a predetermined change in the inputs.

- Security, or the ability to provide changes in the output conditions only when certain specified changes take place at the inputs.

- Availability, or the ability to remain in the "ready to operate" mode.

- Maintainability, or the ability to pass easily from a faulty state to a healthy state.

- Simplicity, or the ability to perform the required functions with ninimum hardware and minimum interaction between subsystems.

- 10. Low cost.

## 1. Utilization

It is a known fact that classical relays (electromechanical and static) are very poorly utilized devices. They are sitting on the lines "watching" for possible faulty conditions, in order to react. Of course, one can say that relays are utilized last since they are connected to the power systems all the time. But, if there is a way to perform the same functions of basic relaying and some other functions at the same time, then utilization of the classical relays is questionable.

CBR systems are devices which are in general intended to perform some functions besides the protection function. Nevertheless, since CBR systems are performing sequential operations as opposed to the parallel operation of analog relays, the calculation burden placed on digital computers is very heavy, and therefore the available time that could be devoted to some other functions would be very small.

MBR systems could introduce a parallel (non-sequential), distributed system and therefore the calculation throughput of the system would be pretty large which implies that there would be significant computational time available for some functions other than the protection function.

#### 2. Accuracy

Classical relays are very much dependent on the "setting" conditions and the accuracy is highly dependent on fixed setting.

CBR systems are capable of performing calculations with very high accuracy, particularly in terms of error correction and estimation procedures. Accuracy of these devices is highly dependent on the algorithm used, and it can be significantly improved by better algorithms.

MBR systems are pretty much in the same range of accuracy as CBR systems speaking in terms of the characteristics mentioned.

Since the highest degree of information is contained in the shape of the signal waveform, and digital devices are capable of examining this shape, they are capable of performing high accuracy calculations. On the other hand, electromechanical relays are acting on the rms, static or the peak values and these values contain less information than the signal wave shape.

## 3. Speed

Classical relays have speeds that range from several cycles (electromechanical) to one cycle, and may operate as fast as 1/4 of a cycle (static relays).

Digital computers are capable of performing required calculations very fast, on the order of one cycle time or less, but since most of the algorithms require information about the signal

gorithm requirements for high speed, the basi technological capabilities of digital computer are met pretty well with a processor having a instruction cycle time on the order of large c less, a memory cycle time in the order of couple of hundred nanoseconds and A/D conversio times in the order of a couple of hundre seconds.

Microprocessor devices were claimed to b slower than digital computer devices, bu bipolar microprocessors can satisfy any of the functional speed requirements given above. O course, the bipolar devices are expensive, bu MOS devices with cycle times under 1 Asec ar also available today. DMH structure usin distributed processing algorithms (DPA's) would provide concurrent processing which could in crease the speed of the required calculations.

## 4. Flexibility

Consideration of flexibility strongly favo digital systems because there is tremendou flexibility in the adjusting and changing o different features, doing that eithe automatically or at least with minor hardwar changes. A MBR system has some additional features of modular expansion of the system's hardware, as well as the system's software and firmware. Special purpose hardware and programmablememories are also available.

## 5. Reliability

Reliability of the classical relaying systems has been questioned. Some surveys [1] showed that within the protection equipment, the relays are the devices most likely to fail to operate, Particularly if they have not operate for a long time, their reliability is questionable.

pidital devices are very reliable devices in general, and also have capability of selfchecking procedures.

CBR systems are very reliable, assuming reasonable software reliability, but some environmental conditions can significantly influence this reliability.

The MBR device is also very reliable but its distributed configuration might introduce some unreliable situations. But if we take into account reliability versus cost considerations, then we can conclude that if the device is cheat then a high degree of redundancy, which can be considered as an improvement in reliability, might be very attractive. Reliability versus availability is also a central issue. Since the MBR device is flexible and allows easy replacement of faulty parts, the Mean Time Between Failures (MTBF) is of less concern than availability. Mean Time to Repair (MTTR) thus becomes a secondary issue if cheap and quick replacement of the erroneous devices can be performed. The relatively small size of the MBF system also allows the possibility of better protection of the system against environmental influences through appropriate shielding solutions.

## 6. Security

This issue is pretty much related to the reliability, availability and the maintainability issues. The particular feature of

The MBR system could be particularly attractive because of the possibility of implementing a modular security software which could be executed in a distributed fashion, concurrently in several locations.

## 7. Availability

In the section on reliability some relations between reliability and availability were emphasized. This relation should be particularly carefully studied as it is related to the DMH concept. Some of the features of interest would be the microprocessor back up devices capable of automatic replacement of the erroneous device as well as highly standardized plug-in microprocessor cards which could be exchanged very quickly.

## 8. Maintainability

It is probably evident that classical relaying devices require less time, skill and money to be repaired than digital devices.

Eventhough the digital devices are very reliable and therefore make the issue of maintainability less critical, it is still evident that very qualified personnel for maintenance purposes are needed.

Microprocessor based systems introduce some new aspects into the maintainability issue. The parts of the system that malfunction can easily, after replacement, be shipped to qualified and well equipped maintenance centers where quick and inexpensive maintenance can be performed. Eventhough the maintenance centers can be geographically separated from the installation location, the transportation facilities and low cost of transportation can still make maintainability highly efficient and considered together with availability and reliability highly flexible and economical.

## 9. Simplicity

It must be admitted that classical relaying equipment and configurations are, compared to the digital relaying systems, fairly simple, but the simplicity has to be in agreement with the level of complexity of the protection system used.

It is the authors' opinion that the DMH concept is logically simpler than any other digital relaying concept. Simplicity of the DMH concept is primarily due to its modular, distributed processing algorithm and its logical breakdown of the required functions by certain levels of functioning.

## 10. Low Cost

Cost is one of the major issues in the field of power system protection and is emplasized in this paper as one of the major issues of the DMH concept, too.

It is an evident fact that the cost of the classical relaying equipment and conventional digital computers have been substantially constant for a long time and do not show any significant trend towards going lower.

Microprocessor devices are showing a tremendous trend towards the lowering of its

It should be noted that these limits are ve low and are coming near prices of \$3.80 p microprocessor chip in quantities and bel \$30.80 per microcomputer on a chip.

Of course the main cost reduction of to DMH system would result from mass production but we are convinced that all other issues (1-1) discussed above should be carefully studied an utilized in order to favor the DMH concept at the less expensive way of protection.

As a conclusion to this section, it should be emphasized that digital protection system are surely more sophisticated systems than the conventional relaying systems. This sophistication should provide a more reliable, secure better utilized, more flexible and accurate protection system.

The other issues like maintainability availability, cost, speed and simplicity are the characteristics that should help distinguis between the digital computer relaying concept and the DMH concept.

In the following section some basic features of the DMH system are discussed and the relation between these features emphasized.

# III. THE DMH SYSTEM-ITS ALGORITHM AND ARCHITECTURE

In order to define the algorithm and the architecture of the DHM system we will at first discuss the functional requirements of the protection function as well as its logical decision structure. This will lead to the definition of the Distributed Processing Algorithm (DPA) and the Distributed Processing Architecture (DPAR) of the DMH system. Normal and abnormal modes of operation of the DMH system are also discussed. Specific characteristics of the proposed DMH system are discussed at the end.

#### Functional Requirements and Logical Decision Structure

Protection of transmission lines, transformers, generators and bus bars as well as some other control and monitoring functions are assumed to be the set of protection functions which our system would handle.

Protection of each of the mentioned power system elements is a local function and can be performed almost entirely locally. The situations which introduce nonlocal requirements are special events, like very serious faults causing damage to the control equipment, etc. Delivery of the collected data, as well as certain backup situations are also nonlocal requirements. Of course, any change of the basic electrical characteristics of the power system being monitored would also require some communication facilities between the local protection systems.

Local protection function can be fairly complex, consisting of several decision functions. Data obtained by sensors could be shared between these decision functions. Therefore, some coordinating function should be performed at the local protection systems.

While performing certain protection functions, the local protection system is actually converting the local data collected by sensors into new data base. This can be viewed as a preprocessing function, preparing data for some quires data from other local systems and/or from the central control system. Therefore a connecting function providing a connection between the local systems and other related systems should also be provided.

It becomes evident that there should exist a point where the concentrating function could be performed. This function will mainly allow the concentration of data preprocessed at local points in order that the concentrating system can analyze the data, as well as make relevant decisions and send them to the local point and elsewhere.

We are assuming that there exists an overall protection function within the power system and therefore some central decision function also exists but, as far as the proposed DNH system is concerned, the problem of the central decision function is beyond the scope of this paper.

## DPA and DPAR of the Proposed DMH System

From the discussion given above we can define the following DPA's:

- There is a set of different algorithms performed by local points. Local point algorithms can be performed concurrently.

- There is a set of coordinating algorithms for each particular protection function which coordinate execution of the local point algorithms.

- Separate algorithms are necessary to handle communications between the local points and the concentrating point. These algorithms are logically dependent and are executed in some arbitrary order.

- 4. A set of algorithms is necessary to coordinate the execution of the algorithms given above (1, 2, 3). Since algorithms 1, 2, and 3 can be performed concurrently, the algorithms of the concentrating point should coordinate possible interactions between algorithms 1, 2 and 3.

- 5. There exists a distributed data base which is preprocessed by algorithms 1, 2 and 3 respectively, and made available to algorithm 4. The data base at each stage of transformation is stored and maintained as a local data base and is unchanged until the moment when the distributed data base is updated as a whole. There exists a set of algorithms which takes care of the described operations that are performed on the distributed data base.

## DPAR characteristics are:

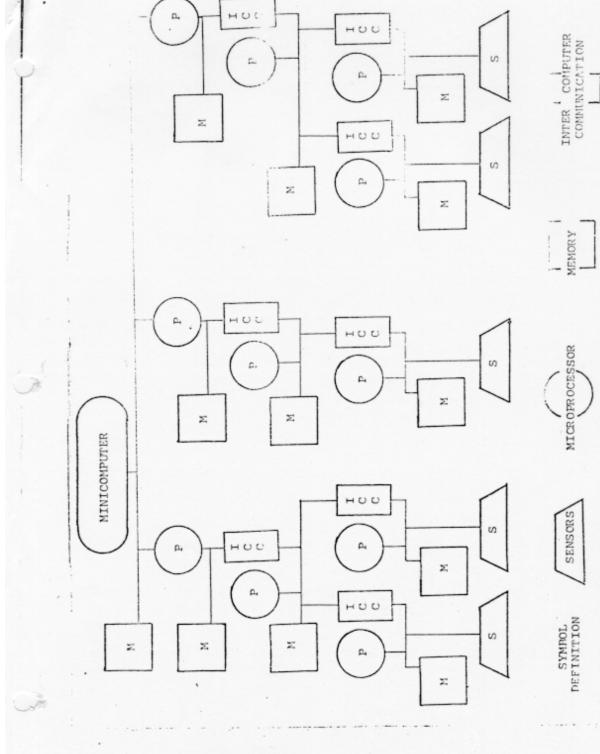

- There are 4 levels in the hierarchy where the following units are located:

- -Local processing units (level 1) -Coordinating units (level 2) -Connecting units (level 3) -Concentrating units (level 4)

- Levels 1, 2 and 3 represent the major part of the DMH system. Level 4 is intended for minimum applications.

- could be implemented using microproces sors.

- The proposed DMH system consisting of levels 1, 2 and 3 is intended for single substation application where level 4 would be monitored by minicomputer. This situation determines the number of units at each level of the DMH system.

- Each level has its own memory storage and it is connected to the common but of that level.

- 5. The flow of information data in the structure is mostly from local points up to the concentrating point. The flow of control data is mostly from the concentrating point down to the local points but in both the mentioned cases there is a possibility of reverse flow of the information and control data.

- Interrupts are issued ordinarily in the direction from level 4 towards level 1 but, on some rare occasions the other direction is also possible but in a stepped fashion from level to level.

- Ordinary, polling and scanning capabilities are used for normal reporting procedures established between levels 1, 2, 3 and level 4.

### Proposed DMH System

The proposed system is represented in Figure 1. The configuration given in Figure 1 operates in two basic modes:

-The normal mode of operation -The abnormal mode of operation

The normal mode of operation assumes, basically, the concurrent operation of local systems with an established procedure for reporting the status data to the concentrating system. The system can be viewed as a transformation system which takes data from the system at level 8 (senors), preprocesses that data, makes some decisions and sends the data to the upper levels. So there exists a transformation and updating of local data bases, while the flow of information is from lower levels to the upper levels. There is an established order as to how the concentrating system takes data from the lower levels, makes decisions and sends back the control data.

The abnormal mode of operation changes, in a sense, the operational characteristics of the system given above. In an abnormal situation one of the local systems detects the abnormality and reports that immediately to the upper levels.

Depending upon the importance and complexity of the abnormal situation, help might be requested through all of the levels up to the concentrating system. In this case, all other local point systems would perform almost totally independent operations, allowing the concentrating system to be devoted to the local point system where the abnormality has occurred. These "independent" local point systems should also be ready to respond to possible unusual requests for information and control data. After the abnormal situation vanishes the restorative mode of operation should establish all the conditions required for the party lade of operation

## Characteristics of the Proposed DMH System

All of the parameters discussed in Section 2 could now be discussed in more detail. However, we will assume that it will be more interesting to summarize some important features of the DMH system which would involve several of the parameters given is Section 2 at the time.

#### These features are:

- The DMH system can be developed as a general system which could be applied to most of the protection environments.

- 2. Hardware structure could be made fully programmable allowing for specific characteristics to be incorporated in the general system.

- protocol Hardwired communications Hardwired communications protocol should be flexible enough to allow fully expandable and flexible microprocessor networks.

- Hierarchical architecture of the microprocessor network provides an op-timal throughput of the data and control messages, and is fully suitable for the logical requirements of the protection function. Deadlock situa-tions are highly unlikely for the given protection flow of interrupts.

- 5. Redundant memory configuration at each level enables a store-and-forward way of transmitting data from local data bases to the central data base. It also allows a data block transfer without placing a great data flow burden on common buses at each level.

- 6. Redundant hierarchical was not particularly discussed, but the standardized network as it is described would allow attachment of any number of redundant pieces of hardware without any particular problems.

Having defined the proposed DMH system, now proceed to develop specifications for the necessary hardware and software, and to provide a preliminary evaluation of available off the shelf products for this application.

## IV. EVALUATION OF AVAILABLE MICROCOMPUTER HARDWARE FOR PROPOSED MDH SYSTEM

This section considers the capability of available hardware relative to the requirements for components of the DMH system as discussed in Sections 2 and 3. The discussion is divided infor components of the DMH system as discussed in Sections 2 and 3. The discussion is divided into consideration of the following subsystems: memory, communications, Input/Output, and the central processors. Two approaches to implementing the DMH system are discussed briefly: the first optimizes the choice of hardware for each of the functions at the integrated circuit chip level, and requires the design of the microcomputer subsystems; the second approach optimizes the choice at the level of available microcomputer systems.

## Memory Subsystems

Memory devices are available today in a wide variety of sizes and technologies such as: 8K, bipolar PROM; 16K, bipolar ROM; MOS EPROM from 16K to 64K; bipolar RAM from 1K to 16K; up nology. The manufacture and sales of memor devices is highly competitive with a larg number of manufacturers participating in thi market. All important products are secon sourced. It is our opinion that the necessar memory components with adequate capacity and products of the components of the components. speed can be selected from off the shelf, dard products, reliability. which have demonstrate

## Communications Subsystems

Prior to several years ago, the design of communications interface for use in compute networking was a major project involving sub stantial time and money. Many of the standar communication functions are now available in on to a few integrated circuit packages such a to a few integrated circuit packages but to a few integrated circuit packages but UART's. It is our opinion that suc packages together with a simple microcompute packages together with a simple microcomputer communication the integrated in the implementation can solve the intercomputer communication problems to be encountered in the implementatio of a DMH system in a cost effective manner.

## Input/Output Subsystems

Integrated circuit packages developed to perform many of the elementar functions of moving information into and out of the computer systems. The Integrated circuit packages have bee the functional blocks of computer systems. Th proposed DMH system requires I/O interface to variety of devices such as: memory, regular an DMA; interrupt handling; data acquisition sub-systems; special processors such as digita filters. It is again our opinion that available integrated circuit packages together with simpl microcomputers can be assembled to provide cos effective programmable I/O subsystems. This ap proach to the design of this computer network i consistent with the design philosophy used for the design of large scale computer the last decade. Again, it is the advent of medium and large scale integration in the manufacture of integrated circuits and microcomputers which makes it possible to apply this ap-proach to the design of systems such as the proposed DMH.

## Central Processor Subsystems

The phrase Central Processor may call to mind the central unit of a large scale computing system. However, the term is used here to iden-tify the units responsible for processing the algorithms used to identify and evaluate the nature of the fault or other abnormality on the electric power system. The following characteristics of microprocessors are important relative to the DMH application:

- Direct Memory Access (DMA) Word Length (WL) Instruction Cycle Time (ICT)

- Programming Language Options (PLO)

- Chip Technology (CT)

- Interrupt Capabilities (IC)

- Second Source Availability (SSA)

- Number of Instructions (NI)

- Microprogramming Option (MO)

The table shown in Figure 2 summarizes The table shown in Figure 2 summarizes the characteristics of currently available microprocessors which might be considered for the implementation of a DNH prototype system. Although it would be convenient from a compatibility point of view, both hardware and software, to select one type microprocessor for all units in the DMH system, it is probable that

WL. MANUFACTURER MODEL CT SSA CF NPPC NI DMA IC PLC 300 bits MHz ADV.MIC.DEV. AM9080A 4 78 ASMB.HL MMOS INTEL.NEC YES YES 500 FAIRCHILD F8 NMOS MOSTEK OPT YES ASMB, HL NO HC:27/ 1802CD HTGHES AIRC. CMOS RCA 8 6.4 1 91 YES YES ASMB NO INTEL 8080A2 TI,AMD 2 YES NO INTEL 8085 MMOS 1 80 YES YES ASMB, HL NO INTEL 8748/ DMA 90 ASMB 6 NMOS NO YES NO 8048 MOTOROLA AMD, HIT., FC AMD, INTEL, TI 6800 NMOS 2 72 OPT YES ASMB, HL NO µPD8080A NMOS 78 YES YES ASMB, HL 80 SIGNETICS 8X300 BiP SMS 8 4 8classes NO NO ZILOG Z80 NMOS MOSTEK YES YES ASMB, HL NO HARRIS SEMI. INTERSIL HM6100A CMOS 12 10 70 YES YES ASMB, HL NO 16 33 PANAFACOM NMOS ASMB L-16 YES YES NO TEXAS INST. TEXAS INST. TMS9900 16 69 -MMOS 3 YES ASMB, HL YES \$BP9900 ASMB, HL 69 YES YES ADV.MIC.DEV. AM2901A RAYT., MOT. 4bS\* 8 1 vsr OPT OPT MICROPROG. YES MONOL.MEM. 6701 B1PS\*\* 4bS 10 MOTOROLA 2900 LSTTL AMD, RAYT 4bS 9.5 unlim OPT YES MICROPROG. YES MOTOROLA 10800 ECL 4bS 12.5 var unlim OPT YES --7 SIGNETICS 3002 BiPS 255 1 40 OPT OPT MICROPROG. YES INTEL TEXAS INST. SBP/0400 512 MICROPROG. 4bS YES YES IIL YES TEXAS INST. 743481 BiP 10 512 YES

\*4bS- 4 bit slice; \*\*BIPS- Bi-polar Schotky

FIGURE 2: TABULATION OF CHARACTERISTICS OF SELECTED MICROPROCESSORS AVAILABLE MAY, 1978

Ē

required in the central processing type functions will require a 16 bit word to provide adequate precision in the arithmetic operation. The use of double precision arithmetic routines would probably limit the utility of the 8-bit processors for this application. On the other hand, it seems likely that the 8-bit processors may prove to be adequate and cost effective in the role of programmed controllers for I/O and communications functions. Special processor type chips have recently become available which type chips have recently become available are designed to perform floating point arith-metic as a hardware function, rather than programming such operations in software. Packages are also available to implement hard-ware subroutines to calculate trignometric and logrithmic functions. These special packages can be utilized if it is necessary to speed up the arithmetic in order to complete the fault analysis algorithms in desired time period.

The table provides a comparison of two difparameters which are related to the speed at which the processor can execute programs. The first is the basic clock frequency (CF) and the second the number of phases per cycle NPPC. It is our opinion that microprocessors can be chosen from those available which will be cost effective for the implementation of a prototype DMH system.

One approach would be to select the nicroprocessor chip which is optimum for each module of the system and design that module as a special purpose microcomputer system. The second is to select appropriate microcomputers as provided by a number of vendors, and develop only the interface circuitry to create the protype modules for the DMH system. Examples of protype modules for the DMH system. Examples of microcomputer boards which are available and candidates for consideration are: INTEL SBC 80/20-4; Data General, micro-NOVA; Digital Equipment Corporation, LSI-11 series; MOSTEK, 2-80 OEM controller; Texas Instruments, 990/4; and MOTOROLA MEC 6820B. We believe that the second approach would be the most cost effective way to create prototype DMH system for evalua-tion and field testing. At the time such a system was to be produced and installed in quantity, the first approach would likely produce the most cost effective system.

## v. CONCLUSION

As a conclusion to our discussion we want to emphasize the following, in our opinion in-teresting, points discussed throughout the paper:

- The main characteristics of the research performed in the field of CR so far is primarily based on single, large scale computer systems (at least 1. The main a minicomputer) and algorithms are not classified as DPA's.

- 2. The introduction of LSI technologies in the early 70's have given some new pos-sibilities to the consideration of the CR as a whole.

- \*3. The DMH concept is a logical and feasible possibility for the implemen-tation of LSI to the CR problem.

- DPA's, functionally divided "ver-tically" and "horizontally", as well as the DPAR of the proposed DMH system, are very suitable for actual protec-tion system requirements.

The hardware needed to implement the properties of microprocomputers is available as off the shelf components today.

This paper evolved from some analysis and studies of the CR field performed in our depart-ment. We are currently in the stage of specifying the design requirements for DPA's and DPAR for the protection of the different ele-ments of the power systems. Some design ac-tivities for the overall protection system based on the DMH concept have already been performed and we are looking forward to publishing the results in a future paper.

- [1] IEEE Bibliography and Publicity Subcon-mittee Report, "Bibliography of Relay Literature", Paper No, 77 500-2, IEEE PES

- Summer Reeting, 1977.

[2] J.G. Gibert, A. Udren, M. Sackin,

"Bibliography of Digital Computer

Relaying Literature", Paper No. 78 114-1,

- The authors maintain their own bibliography which contains around 100 titles related to the digital computer

- relaying.

[4] Dash, P.K. and Mathur, R.M., "A Microcomputer Based Control of Power Systems",

International Symposium on Mini and

- Microcomputers, Nov. 8-11, 1976.

[5] Kezunovic, M., "A Microprocessor Based Substation System: Some Basic Considera-

- tions", M.Sc. Theseis, University of Kan-sas, 1977.

[6] Miki, Y., Sano, Y., Makino, J.I., "A Study of High Speed Distance Relay Using 9 Microcomputer", IEEE Transactions on Power Apparatus and Systems, v 96 \$2, 1977. 1977.

- [7] Rummer, D.I., Kezunovic, M., "A Distributed Processing Microprocessor based Rierarchically Structured (DMH) Relaying System - Some Basic Considera-tions\*, Proceedings of the Energy '78 IEEE Region 5 Annual Conference, Tulsa, Oklahoma, April 1978. [8] - Russel, B., "A Microprocessor Based Sub-

- [8] Russel, B., "A Microprocessor Based Sub-station Control System", Ph.D. Disserta-tion, University of Oklahoma, 1975. [9] Russell, B.D., Miller, R.P., "Microprocessor Algorithm for Overcurrent Protection of Distribution Systems", Conof Power Systems Conference, Record

- of Papers 1978.

Russell, B.D., "Present and Future Applications of Microcomputers in Power System Control", Microcomputers '77, Conference Record. April 1977

| 0.1          | NO NO NO                     | NO<br>NO<br>NO                    | N 00 1                                    | NO<br>NO<br>NO                     | 7<br>YES                                   | YES                                | YES                                     |

|--------------|------------------------------|-----------------------------------|-------------------------------------------|------------------------------------|--------------------------------------------|------------------------------------|-----------------------------------------|

| PLC          | ASMB, HL<br>ASMB, HL<br>ASMB | ASMB, HL<br>ASMB, HL<br>ASMB      | ASMB, HL<br>ASMB, HL                      | ASMB, HL<br>ASMB, HL<br>ASMB       | ASMB, HL<br>ASMB, HL<br>MICROPROG.         | MICROPROG.                         | MICROPROG.                              |

| IC           | YES                          | YES<br>YES<br>YES                 | YES<br>YES<br>NO                          | YES<br>YES                         | YES                                        | YES                                | OPT<br>YES<br>YES                       |

| DMA          | YES<br>OPT<br>YES            | YES<br>YES<br>NO                  | YES                                       | YES                                | YES                                        | TGO T                              | OPT<br>YES<br>YES                       |

| IN           | 78<br>70<br>91               | 78<br>80<br>90                    | 72<br>78<br>8classes                      | 158<br>70<br>33                    | 69<br>69<br>var                            | 36<br>unlim<br>unlim               | 40<br>512<br>512                        |

| NPPC         | 2                            | 1 1 5                             | 4 5 5                                     | 10 2                               | 7 7 7                                      | 10<br>var                          |                                         |

| CF           | 4<br>2<br>6.4                | 269                               | 404                                       | 7 8 7                              | e e e                                      | 10<br>9.5<br>12.5                  | 10                                      |

| WL           | ග ස භ                        | ဆထထ                               | 80 80                                     | 8<br>12<br>16                      | 16<br>16<br>4bS*                           | 465<br>465<br>465                  | 265<br>465<br>465                       |

| SSA          | INTEL,NEC<br>MOSTEK<br>RCA   | TI, AMD                           | AMD, HIT., FC<br>AMD, INTEL, TI<br>SMS    | MOSTEK<br>INTERSIL                 | MOT.                                       | AMD, RAYT                          | INTEL                                   |

| 5            | NMOS                         | NMOS                              | NMOS<br>NMOS<br>BAP                       | NAMOS<br>CMOS<br>NAMOS             | NMOS<br>IIL<br>RAYI.,MOI.                  | BIPS**<br>LSTTL<br>ECL             | BIPS                                    |

| MODEL        | AM9080A<br>F8                | 1802CD<br>8080AZ<br>8085<br>8748/ | 8048<br>8048<br>6800<br>µPD8080A<br>8x300 | 280<br>HMG100A<br>L-16             | 3BP9900<br>AM2901A                         | 6701<br>2900<br>10800              | 3002<br>SBP/0400<br>743481              |

| MANUFACTURER | ADV.MIC.DEV.<br>FAIRCHILD    | INTEL INTEL                       | HOTOROLA<br>NEC                           | ZILOG<br>HARRIS SEMI.<br>PANAFACOM | TEXAS INST.<br>TEXAS INST.<br>ADV.MIC.DEV. | MONOL.NEM.<br>MOTOROLA<br>MOTOROLA | SIGNETICS<br>TEXAS INST.<br>TEXAS INST. |

\*4bS- 4 bit slice; \*\*BiPS- Bi-polar Schotky

TABULATION OF CHARACTERISTICS OF SELECTED MICROPROCESSORS AVAILABLE MAY 1978 FIGURE 3:

FIGURE 1: INCOCK DIAGRAM OF A DISTRIBUTED PROCESSING MICROPROCESSOR BASED HIBRARCHICALLY